# Debugging Formal Specifications \*

# A Practical Approach using Model-Based Diagnosis and Counterstrategies

Robert Könighofer, Georg Hofferek, Roderick Bloem

Institute for Applied Information Processing and Communications (IAIK), Graz University of Technology, Austria.

Received: date / Revised version: date

**Abstract.** Creating a formal specification for a design is an error-prone process. At the same time, debugging incorrect specifications is difficult and time-consuming. In this work, we propose a debugging method for formal specifications that does not require an implementation.

We handle conflicts between a formal specification and the informal design intent using a simulation-based refinement loop, where we reduce the problem of debugging overconstrained specifications to that of debugging unrealizability. We show how model-based diagnosis can be applied to locate an error in an unrealizable specification. The diagnosis algorithm computes properties and signals that can be modified in such a way that the specification becomes realizable, thus pointing out potential error locations. In order to fix the specification, the user must understand the problem. We use counterstrategies to explain conflicts in the specification. Since counterstrategies may be large, we propose several ways to simplify them. First, we compute the counterstrategy not for the original specification but only for an unrealizable core. Second, we use a heuristic to search for a countertrace, i.e., a single input trace which necessarily leads to a specification violation. Finally, we present the countertrace or the counterstrategy as an interactive game against the user, and as a graph summarizing possible plays of this game. We introduce a user-friendly implementation of our debugging method and present experimental results for GR(1) specifications.

### 1 Introduction

Ideally, a formal specification for a design is written before the design is implemented. This establishes an un-

ambiguous notion of correctness, which can be used as an objective during the implementation phase. It also makes the informal design intent precise, thus preventing misunderstandings between collaborating designers. Clearly, the specification must have the highest possible quality when used as correctness objective for the implementation. The process of deriving an implementation from the formal specification can also be automated using property synthesis techniques [40,31,24,39, 17,36]. This yields implementations which are correct by construction with respect to the formal specification. In such a synthesis-based design flow, a high quality specification is even more crucial since the synthesized implementation can only be as correct as its specification.

Formal specifications are also created and sold as intellectual property for verification [15]. In this scenario, too, a specification has to be created that reflects exactly the informal design intent without a corresponding implementation being available.

Like other engineering processes, constructing a high quality formal specification is a difficult task [25,38,12,22,11], especially if no implementation is present. Mistakes can lead to various flaws. First, a specification may be incomplete. This means that the specification allows implementations that do not conform to the informal design intent. Second, the specification may be unsound. This is the case if it disallows implementations that are valid with respect to the design intent. As a special case, the specification may be unrealizable. An unrealizable specification does not allow any implementation. In this article we introduce debugging techniques for unrealizability and unsoundness.

It is possible to turn an unsound specification into an unrealizable one by adding properties to enforce the desired behavior that is forbidden by the specification. We use this idea to reduce the problem of debugging unsound specifications to the problem of debugging unrealizable specifications. However, unrealizability is also

$<sup>^\</sup>star$  This work was supported in part by the European Commission through the projects COCONUT (FP7-2007-IST-1-217069) and DIAMOND (FP7-2009-IST-4-248613)

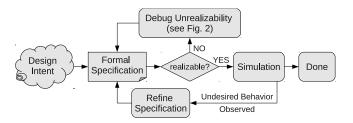

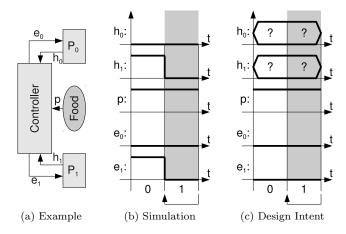

Fig. 1: Refining a specification.

a serious problem of its own. Our experience in writing complete formal specifications (e.g., [3,4]) for property synthesis tools shows that many mistakes during specification development lead to unrealizability. Debugging an unrealizable specification is difficult. Even an enormous piece of software can be executed to track down the error, but this is not possible for an unrealizable specification. It is important to note that, for systems with inputs and outputs, there is a difference between the realizability and the satisfiability of a specification. A specification is satisfiable if one trace of input values and output values fulfilling the specification exists. This is a necessary but not a sufficient condition for realizability. A specification is only realizable if there is a valid output trace for every possible input trace. Additionally, the outputs in any particular time step may depend on past and present inputs only. Tools such as RAT [38] explain why a single trace does not conform to the specification. However, this does not suffice to explain unrealizability.

# Context

In this work, we address the debugging of specifications for reactive systems. A reactive system is a system which interacts with its environment via inputs and outputs in an infinite execution. Our debugging method is based on the synthesis of reactive systems conforming to a given specification, and on the synthesis of corresponding counterstrategies. We assume specifications to consist of environment assumptions and system guarantees: If the environment fulfills all assumptions, then the specification requires the system to fulfill all guarantees. Our debugging approach can deal with a wide range of such specifications. In addition to a general description, we also explain how it can be applied to Generalized Reactivity(1) [39]. For the latter, synthesis is performed using fixpoint computations over states in a game graph, implemented symbolically using BDDs [6]. Our debugging technique analyzes specifications stand-alone, i.e., it does not require a corresponding implementation.

# Outline of our Debugging Approach

This article is based on [27], [29], [2], and [28]. We propose the flow depicted in Fig. 1 to create a high quality

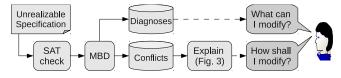

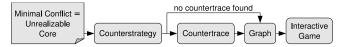

Fig. 2: Our approach to debug unrealizability.

specification. The user creates an initial formal specification of the design. If the specification is unrealizable, it needs to be debugged. If the specification is realizable, it can be simulated. If undesired behavior (with respect to the informal design intent) is observed during simulation, the specification is refined to exclude this undesired behavior. The refined specification can be realizable or unrealizable again. This is repeated until the user is satisfied with the behavior of the design.

Unrealizability is debugged as illustrated in Fig. 2. First, we check for satisfiability. If the specification is unsatisfiable, existing trace-based debugging methods [38] can be applied. However, since unsatisfiability is a special case of unrealizability, our debugging method works in any case. Next, we use model-based diagnosis [41,26] (MBD) to identify possible error locations in the specification. In order to apply MBD, we take the unrealizable specification as an inherently conflicting model. As diagnoses we get sets of guarantees and outputs that can be weakened in order to make the specification realizable. The computation of diagnoses relies on the computation of minimal conflicts in the specification. Minimal conflicts are unrealizable cores, i.e., minimal subsets of the specification which are unrealizable on their own. Diagnoses indicate possible error locations. However, in order to be able to find the best repair for unrealizability, the user additionally has to understand the problem.

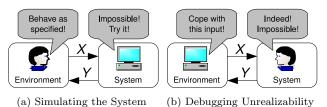

Explaining unrealizability means to explain why no implementation can fulfill the specification. We cannot explain for every possible implementation why it does not conform to the specification. However, the user must have an implementation in his mind when creating the formal specification. We show that this imagined implementation does not conform to the formal specification by swapping the roles between the tool and the user as illustrated in Fig. 3. The tool takes on the role of the environment and the user takes the role of the system. The two parties play a diagnostic game: The tool provides inputs and the user tries to provide outputs that conform to the specification. Since the specification is unrealizable, there exists a so-called *counterstrategy* for the environment, which makes the user fail for sure. However, while trying, she will understand why there is no way to fulfill the specification, i.e., why the specification is unrealizable. This knowledge can then be used to correct the specification.

In general, a counterstrategy cannot be presented as a single trace of inputs, since inputs may depend on

Fig. 3: Explaining unrealizability by swapping the roles.

previous outputs. Our experience shows that these dependencies can become quite complex, especially for a large unrealizable specification. This makes it difficult for the user to comprehend which environment behavior leads to problems and why the specification is unrealizable. We therefore propose several techniques to simplify counterstrategies. First, we compute the counterstrategy not for the original specification, but for an unrealizable core. Every unrealizable core contains one root cause of unrealizability. Explaining unrealizable cores instead of the entire unrealizable specification allows the user to focus on one problem at a time. When computing unrealizable cores, we not only remove properties but also signals from the specification. This allows the user to focus on those signals that are relevant for the conflict when playing the diagnostic game. Second, we attempt to compute what we call a *countertrace*. A countertrace is a single trace of inputs such that no behavior of the system can fulfill the specification. A countertrace does not always exist. Even if one exists, its computation is often expensive. Hence, we present a heuristic.

This article is organized as follows. Section 2 discusses related work. Section 3 gives definitions and establishes notation. In Section 4, we describe our debugging approach in a generic way; we elaborate it for Generalized Reactivity(1) [39] specifications in Section 5. An implementation in the requirements analysis and synthesis tool RATSY [2] is presented in Section 6. Section 7 presents experimental results and Section 8 concludes.

# 2 Related Work

Incomplete specifications and coverage metrics have already been addressed before in various ways. There is existing work on completeness checking with respect to a given implementation. This includes the definition of different comparison criteria between the tableau of the specification and the implementation [25], identification of parts of the state space of the implementation which are covered by the specification [23], and checking if modifications introduced into the model of the implementation are detected by the specification [8,9]. On the other hand, there are methods for coverage analysis that do not rely on a particular implementation. A notion of "forgotten cases", which are situations where a

certain output in a certain time step is not constrained, is introduced in [12]. Another concept is that of *inherent* vacuity [18]. A specification is inherently vacuous if it can be mutated into a simpler but equivalent specification. Other work checks the specification with respect to a high-level fault model by testing if an implementation which contains stuck-at faults can still conform to the specification [14]. Our debugging approach allows the user to eliminate incompleteness that shows up in simulation. Apart from that, we do not specifically address incomplete specifications. Rather, we focus on specifications which are unsound.

Model-based diagnosis [26,41], which was originally invented to automate debugging of misbehaving physical systems, has already been applied for diagnosis in various settings such as logic programs [13], functional programs [46], VHDL designs [20], Java programs [35], knowledge bases [16], and ontologies [19]. We use model-based diagnosis to perform error localization in unrealizable specifications of reactive systems. This deviates from the standard setting in that there is no observation contradicting a system description, but only an inherently conflicting system description. Our method is similar to [34], where hitting sets are used to compute all unsatisfiable cores in an unsatisfiable constraint system.

Yoshiura [49] addresses the problem of debugging unrealizable specifications by defining several bug localization heuristics based on a classification (into strong satisfiable, stepwise satisfiable, and stepwise strong satisfiable) and the tableau of the specification. Their objective is similar to ours, but there are few similarities in methodology. Cimatti et al. [11] propose to present an unrealizable core as diagnostic aid for unrealizability. Our work extends theirs: We use unrealizable cores for diagnoses computation and to obtain more focused counterstrategies. As an improvement, we not only remove properties but also signals from the specification. Furthermore, we use Delta Debugging [50] as a more advanced and often faster algorithm for unrealizable core computation. While single unrealizable cores help to understand problems in the specification, they are less useful for suggesting locations to fix them. The reason is that many unrealizable cores may exist, and that a repair has to resolve them all. We address this problem with the model-based diagnosis step, which takes all unrealizable cores into account.

Counterstrategies have been used or at least mentioned as debugging aids for unrealizability in various settings such as game graphs with controllable and uncontrollable edges [48], Live Sequence Charts [5], timed automata [1], and for model-checking of the modal  $\mu$ -calculus [45,44] with more efficient algorithms and implementations presented in [32,33,47]. None of these papers mention the simplification of counterstrategies in order to provide the user with helpful diagnostic information. This is one of the main contributions of our work. In particular, we are not aware of any previous

work on countertraces. Also, we do not know of any existing publication showing how unsound specifications can be debugged with counterstrategies.

### 3 Preliminaries

### 3.1 Model-Based Diagnosis

Model-based diagnosis (MBD) [26,41] is a method to identify possible error locations in a system. In this work, we follow the definitions and notation of [41]. Let SD be a description of the correct behavior of a system, and let OBS be an observation of an erroneous behavior. Both SD and OBS are sets of logical sentences. The system is assumed to consist of a set COMP of components. Every component  $c \in \mathsf{COMP}$  can behave abnormally (denoted AB(c)) or normally (denoted  $\neg AB(c)$ ). The behavior of a component c is described with a logical sentence of the form  $\neg AB(c) \Rightarrow N_c$ , where  $N_c$  defines the normal behavior of c. That is, if the component behaves abnormally, it can exhibit any behavior. The system description SD consists of component descriptions and a definition of their interconnections or interplay, again in terms of logical sentences. The observation OBS is in contradiction with the system description. That is, if all components behaved normally, it would be impossible to observe OBS. More formally, the set  $SD \cup OBS \cup {\neg AB(c) \mid c \in COMP}$  of logical sentences is inconsistent, i.e., contains a logical contradiction. We write  $\neg$  consistent(SD  $\cup$  OBS  $\cup$  { $\neg$  AB(c) |  $c \in$  COMP}) to express this.

MBD identifies sets of components that may have caused the erroneous behavior OBS. Such sets are called diagnoses. Formally, a set  $\Delta \subseteq \mathsf{COMP}$  is a  $\mathit{diagnosis}$  iff it is a minimal set of components such that

$$consistent(SD \cup OBS \cup \{\neg AB(c) \mid c \in COMP \setminus \Delta\}) \quad (1)$$

holds. Minimality means that Eq. 1 must not hold for any subset  $\Delta' \subset \Delta$ . Thus, the observation would be possible under the assumption that all components in a diagnosis behaved abnormally. Hence, every diagnosis represents a fault candidate. A diagnosis  $\Delta$  with  $|\Delta|=1$  is called a *single-fault diagnosis*.

Diagnoses can be computed using conflicts. A conflict is a set  $C \subseteq \mathsf{COMP}$  such that

$$\neg \operatorname{consistent}(\mathsf{SD} \cup \mathsf{OBS} \cup \{\neg \operatorname{\mathsf{AB}}(c) \mid c \in C\}) \tag{2}$$

holds. Informally speaking, a conflict is a set of components that cannot all behave normally. If all components of a conflict behaved normally, the observation would be impossible. Again, a conflict C is minimal if no subset  $C' \subset C$  is a conflict. A diagnosis must explain all conflicts, so it must share at least one element with every conflict. This relation can be formalized using hitting sets. A  $hitting\ set$  for a collection K of sets is a set H

such that  $\forall K \in \mathcal{K} . H \cap K \neq \emptyset$  holds. A hitting set H is minimal if no subset  $H' \subset H$  is a hitting set for that collection. A set  $\Delta \subseteq \mathsf{COMP}$  is a diagnosis iff  $\Delta$  is a minimal hitting set for the collection of all minimal conflicts. Hence, computing diagnoses reduces to computing minimal hitting sets for the collection of minimal conflict sets. Reiter [41] presents an algorithm for minimal hitting set computation which computes conflicts on-the-fly and produces diagnoses in order of increasing cardinality. Diagnoses with a lower cardinality are in general considered as more likely fault candidates than diagnoses with higher cardinality. Thus, if the algorithm is aborted before all diagnoses have been computed (which is often the case), only less likely fault candidates are missed.

#### 3.2 Automata and Machines

A deterministic and complete Büchi word automaton (a DBW) is a tuple  $\mathcal{A} = (Q, \Sigma, T, q_0, F)$ , where Q is a finite set of states,  $\Sigma$  is a finite alphabet,  $T: Q \times \Sigma \to Q$  is a deterministic and complete transition function,  $q_0 \in Q$ is the initial state, and  $F \subseteq Q$  is a set of accepting states. A run of the automaton A on an (infinite) word  $\overline{\sigma} = \sigma_0 \sigma_1 \sigma_2 \dots \in \Sigma^{\omega}$  is an infinite sequence of states  $\overline{r} = q_0 q_1 q_2 \ldots \in Q^{\omega}$  such that  $q_{i+1} = T(q_i, \sigma_i)$  for all  $i \geq 0$ . The run is accepting iff  $\inf(\bar{r}) \cap F \neq \emptyset$ , where  $\inf(\overline{r})$  denotes the states occurring infinitely often in  $\overline{r}$ . Given two disjoint sets of Boolean inputs and outputs X and Y, we assume that  $\Sigma = \mathcal{X} \times \mathcal{Y}$  is composed of an input alphabet  $\mathcal{X} = 2^X$  and an output alphabet  $\mathcal{Y} = 2^{Y}$ . Moreover, we assume that  $Q = 2^{V}$  for a set V of state bits. This allows for symbolic representations using BDDs [6]. For an input trace  $\overline{x} = x_0 x_1 \dots \in \mathcal{X}^{\omega}$ and an output trace  $\overline{y} = y_0 y_1 \dots \in \mathcal{Y}^{\omega}$ , we write  $\overline{x} || \overline{y}$  to denote the composition  $(x_0, y_0)(x_1, y_1) \dots \in \Sigma^{\omega}$ .

A Mealy machine is a tuple  $M^e = (Q, \mathcal{X}, \mathcal{Y}, \delta, q_0, \lambda)$ , where  $Q, \mathcal{X}, \mathcal{Y}$ , and  $q_0$  are defined as for DBWs,  $\delta: Q \times \mathcal{X} \to Q$  is a complete transition function, and  $\lambda: Q \times \mathcal{X} \to \mathcal{Y}$  is a complete output function. Given the input trace  $\overline{x} = x_0 x_1 \ldots \in \mathcal{X}^\omega$ ,  $M^e$  produces the output trace  $M^e(\overline{x}) = \lambda(q_0, x_0)\lambda(q_1, x_1) \ldots \in \mathcal{Y}^\omega$ , where  $q_0 q_1 \ldots \in Q^\omega$  is a sequence of states with  $q_{i+1} = \delta(q_i, x_i)$  for all  $i \geq 0$ . We denote the set of words that can be produced by  $M^e$  by  $L(M^e) = \{\overline{x} | | \overline{y} \in (\mathcal{X} \times \mathcal{Y})^\omega \mid M^e(\overline{x}) = \overline{y}\}$ .

A Moore machine is a tuple  $M^o = (Q, \mathcal{Y}, \mathcal{X}, \epsilon, q_0, \kappa)$  with  $\epsilon : Q \times \mathcal{Y} \to Q$  and  $\kappa : Q \to \mathcal{X}$ . Given the trace  $\overline{y} = y_0 y_1 \ldots \in \mathcal{Y}^\omega$ ,  $M^o$  produces the trace  $M^o(\overline{y}) = \kappa(q_0)\kappa(q_1)\ldots \in \mathcal{X}^\omega$ , where  $q_{i+1} = \epsilon(q_i, y_i)$  for all  $i \geq 0$ . We have that  $L(M^o) = \{\overline{x} | | \overline{y} \in (\mathcal{X} \times \mathcal{Y})^\omega \mid M^o(\overline{y}) = \overline{x}\}$ . Refer to [21] for a more gentle introduction to automata.

### 3.3 Games

A (finite state, two player) game is a five-tuple  $\mathcal{G} = (Q, \Sigma, T, q_0, \mathsf{Win})$ , where  $Q, \Sigma = \mathcal{X} \times \mathcal{Y}, T$ , and  $q_0$  are defined as for DBWs, and  $\mathsf{Win} : Q^\omega \to \{\mathsf{false}, \mathsf{true}\}$  is

the winning condition. The game is played by two players, the environment and the system. A play  $\overline{\pi}$  of  $\mathcal{G}$  is an infinite sequence  $\overline{\pi} = q_0 q_1 q_2 \dots \in Q^{\omega}$  of states with  $q_{i+1} = T(q_i, \sigma_i)$  for all  $i \geq 0$ . In each step, the letter  $\sigma_i = (x_i, y_i)$  is chosen by the two players in such a way that the environment first chooses an  $x_i \in \mathcal{X}$ , after which the system chooses some  $y_i \in \mathcal{Y}$ . A play is won by the system iff Win $(\overline{\pi})$  = true. Otherwise, it is lost for the system and won for the environment. A (finite memory) strategy for the environment in game  $\mathcal{G}$  is a tuple  $\mathcal{S} = (\Gamma, \gamma_0, \rho)$ , where  $\Gamma$  is some (finite) set representing the memory,  $\gamma_0 \in \Gamma$  is the initial memory content, and  $\rho \subseteq (Q \times \Gamma \times \mathcal{X} \times \Gamma)$  is a relation mapping a state of  $\mathcal{G}$  and the memory content to a set of possible next inputs and an updated memory content. A strategy is deterministic iff  $\forall q, \gamma . |\{(q, \gamma, x, \gamma') \in \rho\}| \leq 1.$

A play  $\overline{\pi}$  conforms to a strategy S iff there exist sequences  $(x_0, y_0)(x_1, y_1) \dots \in \Sigma^{\omega}$  and  $\gamma_0 \gamma_1 \dots \in \Gamma^{\omega}$ such that, for all  $i \geq 0$ ,  $(q_i, \gamma_i, x_i, \gamma_{i+1}) \in \rho$  and  $q_{i+1} =$  $T(q_i,(x_i,y_i))$ . Strategy  $\mathcal{S}$  is winning for the environment from a state  $q_s$  if all plays starting in  $q_s$  and conforming to S are won by the environment. The set  $W^{\text{env}} \subseteq Q$ of states from which such a winning strategy exists is called the winning region of the environment. A counterstrategy is a winning strategy for the environment from  $q_0$ . A counterstrategy exists if  $q_0 \in W^{\text{env}}$ . A trace  $(x_0,y_0)(x_1,y_1)\ldots \in \Sigma^{\omega}$  conforms to a strategy S in  ${\mathcal G}$  iff there exists a play  $\overline{\pi} = q_0 q_1 \dots$  and a sequence  $\gamma_0 \gamma_1 \ldots \in \Gamma^{\omega}$  such that  $(q_i, \gamma_i, x_i, \gamma_{i+1}) \in \rho$  and  $q_{i+1} =$  $T(q_i,(x_i,y_i))$  for all  $i\geq 0$ . The set of traces that conform to S in G is denoted L(G,S). A Moore machine  $M^o$ implements a deterministic strategy S in G iff  $L(M^o) =$  $L(\mathcal{G},\mathcal{S})$ . A construction of  $M^o$  is straightforward. A nondeterministic strategy has to be determinized beforehand. See [21] for a more comprehensive introduction.

### 3.4 $\mu$ -Calculus

The (propositional)  $\mu$ -calculus [30] extends propositional logic with a least fixpoint operator  $\mu$  and a greatest fixpoint operator  $\nu$ . We further extend it by two preimage operators  $\mathsf{MX}^s$  and  $\mathsf{MX}^e$  and use it to describe fixpoint computations over sets  $Q' \subseteq Q$  of states in a game  $\mathcal{G} = (Q, \Sigma, T, q_0, \mathsf{Win})$ .

Let Var be a set of variables ranging over subsets of Q. The syntax of  $\mu$ -calculus formulas can be defined inductively as follows: Every variable  $Z \in \text{Var}$  and every set  $Q' \subseteq Q$  of states is a  $\mu$ -calculus formula. Given that R and S are  $\mu$ -calculus formulas, then so are  $\neg R$ ,  $R \cup S$ , and  $R \cap S$ , with the expected semantics. Finally, for  $Z \in \text{Var}$ , we have that  $\mu Z \cdot R(Z)$ ,  $\nu Z \cdot R(Z)$ ,  $\text{MX}^s(R)$ , and  $\text{MX}^e(R)$  are  $\mu$ -calculus formulas. These are defined as

$$\mu Z.R(Z) = \bigcup_{i} Z_{i}, \text{ with } Z_{0} = \emptyset \text{ and } Z_{i+1} = R(Z_{i}), \quad (3)$$

$$\nu Z.R(Z) = \bigcap_{i} Z_{i}, \text{ with } Z_{0} = Q \text{ and } Z_{i+1} = R(Z_{i}),$$

$$\begin{split} \mathsf{MX}^s(R) &= \left\{ q \in Q \mid \forall x \in \mathcal{X} \, . \, \exists y \in \mathcal{Y} \, . \, T(q,(x,y)) \in R \right\}, \\ \mathsf{MX}^e(R) &= \left\{ q \in Q \mid \exists x \in \mathcal{X} \, . \, \forall y \in \mathcal{Y} \, . \, T(q,(x,y)) \in R \right\}. \end{split}$$

We will refer to the sets  $Z_i$  as the iterates of the fixpoint. The operation  $\mathsf{MX}^s(R)$  gives all states from which the system is able to force the play into a state of R in one step. Analogously,  $\mathsf{MX}^e(R)$  gives all states from which the environment can enforce a visit to R in one step.

# 3.5 Specifications for Reactive Systems

A reactive system is a Mealy machine that continuously interacts with its environment via inputs X and outputs Y. The specifications we consider are of the form  $\varphi = (A,G)$ , where A is a set of environment assumptions and G is a set of system guarantees. Let  $\overline{\sigma} \models p$  denote that a trace  $\overline{\sigma} \in \Sigma^{\omega}$  fulfills an assumption or guarantee  $p \in A \cup G$ . Then  $\overline{\sigma}$  fulfills  $\varphi = (A,G)$ , written  $\overline{\sigma} \models \varphi$ , iff

$$(\forall a \in A . \overline{\sigma} \models a) \text{ implies } (\forall g \in G . \overline{\sigma} \models g).$$

(4)

We assume that properties  $\top$  and  $\bot$  can be formulated with  $\overline{\sigma} \models \top$  and  $\overline{\sigma} \not\models \bot$  for any  $\overline{\sigma} \in \Sigma^{\omega}$ . A Mealy machine  $M^e$  implements a specification  $\varphi$  iff  $\overline{\sigma} \models \varphi$  holds for all  $\overline{\sigma} \in L(M^e)$ . A specification  $\varphi$  is unrealizable, iff no Mealy machine implements it.

A Generalized Reactivity(1) specification [39] (we will write GR(1)) is an instance of a specification of the form (A,G). It consists of m DBWs  $\mathcal{A}_i^e = (Q_i^e, \Sigma, T_i^e, q_{0,i}^e, F_i^e)$  representing the environment assumptions, and n DBWs  $\mathcal{A}_j^s = (Q_j^s, \Sigma, T_j^s, q_{0,j}^s, F_j^s)$  representing the system guarantees. A trace  $\overline{\sigma} \in \Sigma^\omega$  fulfills assumption or guarantee  $\mathcal{A}$  if the corresponding run is accepting in  $\mathcal{A}$ . A game  $\mathcal{G}^{\text{GR1}} = (Q, \Sigma, T, q_0, \text{Win})$  can be built with state space  $Q = Q_1^e \times \cdots \times Q_m^e \times Q_1^s \times \cdots \times Q_n^s$ , transition function  $T((q_1^e, \ldots, q_n^s), \sigma) = (T_1^e(q_1^e, \sigma), \ldots, T_n^s(q_n^s, \sigma))$ , and initial state  $q_0 = (q_{0,1}^e, \ldots, q_{0,n}^s)$ . Let  $J_i^e = \{(q_1^e, \ldots, q_n^s) \mid q_i^e \in F_i^e\}$  be the set of all states of  $\mathcal{G}^{\text{GR1}}$  that are accepting in  $\mathcal{A}_i^e$ . Similarly, let  $J_j^s$  be the set of all states of  $\mathcal{G}^{\text{GR1}}$  that are accepting in  $\mathcal{A}_i^e$ . Then  $\text{Win}(\overline{\pi})$  is true iff

$(\forall i . \mathsf{inf}(\overline{\pi}) \cap J_i^e \neq \emptyset) \text{ implies } (\forall j . \mathsf{inf}(\overline{\pi}) \cap J_j^s \neq \emptyset).$  (5)

The winning region  $W_{\text{sys}}^{\text{GR1}}$  of the system is [39]

$$W_{\text{sys}}^{\text{GR1}} = \nu Z \cdot \bigcap_{j=1}^{n} \mu Y \cdot \bigcup_{i=1}^{m} \nu X \cdot (J_{i}^{s} \cap \mathsf{MX}^{s}(Z)) \cup \mathsf{MX}^{s}(Y) \cup (\neg J_{i}^{e} \cap \mathsf{MX}^{s}(X)) . \tag{6}$$

The result of the greatest fixpoint in X contains all states from which the system can enforce that the play either stays in  $\neg J_i^e$  for some i or eventually reaches the set  $J_j^s \cap \mathsf{MX}^s(Z) \cup \mathsf{MX}^s(Y)$ . Both cases are winning for the system. The former means that an assumption is violated. The latter is winning because the fixpoints in Y and Z ensure that all sets  $J_j^s$  of accepting states of the system can be visited infinitely often, thus fulfilling all guarantees. The winning region for the environment is  $W_{\mathrm{env}}^{\mathrm{GR1}} = Q \setminus W_{\mathrm{sys}}^{\mathrm{GR1}}$ . A GR(1) specification is realizable iff  $q_0 \in W_{\mathrm{sys}}^{\mathrm{GR1}}$  in the corresponding game.

# 3.6 Failure Preserving Minimization Algorithms

We will use two different algorithms to compute minimal unrealizable cores.

Delta Debugging [50] is an algorithm to isolate the trigger of a failure. Given a procedure test and some input C that makes test fail (denoted  $\operatorname{test}(C) = \mathbf{X}$ ), the algorithm computes a minimal input  $\hat{C} = \operatorname{ddmin}^{\operatorname{test}}(C)$  with  $\hat{C} \subseteq C$  such that test still fails on  $\hat{C}$ . We assume that test is monotonic, i.e., that for all  $C'' \subseteq C' \subseteq C$  we have that  $\operatorname{test}(C'') = \mathbf{X}$  implies  $\operatorname{test}(C') = \mathbf{X}$ . The Delta Debugging algorithm is defined as  $\operatorname{ddmin}^{\operatorname{test}}(C) = \operatorname{ddmin}^{\operatorname{test}}(C, 2)$ , with  $\operatorname{ddmin}^{\operatorname{test}}(C', n) =$

$$\begin{cases} \operatorname{ddmin}_2^{\operatorname{test}}(C_i',2) & \text{if } \exists i \operatorname{.test}(C_i') = \mathbf{X} \\ \operatorname{ddmin}_2^{\operatorname{test}}(\overline{C_i'}, \max(n-1,2)) & \text{else if } \exists i \operatorname{.test}(\overline{C_i'}) = \mathbf{X} \\ \operatorname{ddmin}_2^{\operatorname{test}}(C', \min(|C'|, 2n)) & \text{else if } n < |C'| \\ C' & \text{otherwise.} \end{cases}$$

The sets  $C'_1,\ldots,C'_n$  form a partition of C' into n (approximately) equally sized parts, and  $\overline{C'_i}=C'\setminus C'_i$ . The procedure  $\operatorname{ddmin}_2$  first tries to find a subset  $C'_i$  which still fails the test. If such a subset is found, it is reduced further by a recursive call. If not, the complements  $\overline{C'_i}$  are tried. If this does not work either, the granularity n for the search is doubled. If n cannot be increased any further, the current set must be minimal. In the best case, the number of calls to test is logarithmic in |C|. In the worst case, it is quadratic in |C|.

The second failure preserving input minimization algorithm we will use is simpler. It is defined as  $\hat{C} = \mathsf{linMin}^{\mathsf{test}}(C) = \mathsf{linMin}^{\mathsf{test}}(C,C)$  with  $\mathsf{linMin}^{\mathsf{test}}(T,R) =$

$$\begin{cases} R & \text{if } T = \emptyset \\ \mathsf{linMin}_2^\mathsf{test}(T \setminus t, R \setminus t) & \text{else if } \mathsf{test}(R \setminus t) = \mathbf{X} \\ \mathsf{linMin}_2^\mathsf{test}(T \setminus t, R) & \text{otherwise}, \end{cases}$$

where t is a randomly chosen element of T. This algorithm, used in [11], attempts to remove one element after the other, thus requiring exactly |C| checks.

# 4 Debugging Approach

In this section, we introduce our debugging technique in a generic way. We assume that the specification consists of a (possibly empty) set of environment assumptions A and a set of system guarantees G, and that it is possible to add and remove guarantees. Furthermore, procedures realizable and sat deciding realizability and satisfiability of a specification are required. We also assume that the specification can be turned into a game  $\mathcal G$  and that a finite memory counterstrategy can be computed in the case of unrealizability. Moreover, we assume that output signals can be existentially quantified in guarantees. All these are rather loose restrictions that apply to many common logics such as LTL, PSL, CTL, or S1S, to name only a few.

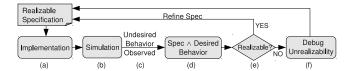

Fig. 4: Our method to fix mismatches with the design intent.

### 4.1 Debugging Undesired Behavior

Deviations of the formal specification from the informal design intent often show up when a system correctly implementing the specification is simulated. If undesired behavior, i.e., behavior that should be forbidden according to the design intent, is observed, then this means that the specification is incorrect and needs to be refined.

Fig. 4 illustrates our method to tackle this problem. Suppose that undesired behavior is observed during the simulation of an implementation of the specification (Fig. 4a-4c). The tool first checks whether the trace fulfills the assumptions. If not, a warning is issued because the system does not need to fulfill any guarantee in this case. Otherwise, the user is asked to specify the desired response to the input trace that was used in simulation. The specification is then augmented with a guarantee enforcing this desired behavior (Fig. 4d). Two cases can be distinguished (Fig. 4e).

- The augmented specification is realizable. That is, the original specification leaves enough freedom to choose either the observed or the desired behavior. It is incomplete and needs to be refined.

- 2. The augmented specification is unrealizable. That is, the original specification disallows the desired behavior because no system can fulfill both. Hence, the original specification is not sound. We debug unsoundness by debugging the unrealizability of the augmented specification (Fig. 4f).

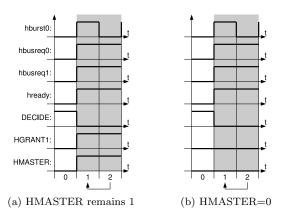

We propose that the user defines the desired behavior simply by modifying the obtained simulation trace. Traces are infinite in our setting, so we assume some finite representation such as a finite stem followed by a loop. We allow the user to change any signal value in any time step to 0, 1, or ?, where ? represents "don't care". Due to the "don't cares", we obtain a trace template  $\overline{t}$ , consisting of an input part  $\overline{t^x}$  and an output part  $\overline{t^y}$ . The user expresses the desired behavior as follows: Whenever the sequence of inputs matches the input part  $\overline{t^x}$  of the template, the outputs have to follow  $\overline{t^y}$ . The use of "don't cares" in  $\overline{t^x}$  and  $\overline{t^y}$  allows the definition of rather general requirements. The tool converts  $\overline{t}$  into a guarantee  $g_{\text{new}}$  enforcing  $\overline{t^y}$  if the inputs conform to  $\overline{t^x}$ .

<sup>&</sup>lt;sup>1</sup> It is also not complete since it allows the undesired behavior that has been observed, but this incompleteness is eliminated by the augmentation.

Fig. 5: Example: Debugging undesired behavior.

More formally,  $\overline{t^x}$  can be seen as a sequence  $t_0^x t_1^x t_2^x \dots$  of functions  $t_i^x: X \to \{0,1,\ref{2}\}$  for all  $i \geq 0$ . Analogously,  $\overline{t^y}$  is a sequence of functions  $t_i^y: Y \to \{0,1,\ref{2}\}$ . A trace  $\overline{\sigma} = (x_0,y_0)(x_1,y_1)\dots \in (\mathcal{X} \times \mathcal{Y})$  conforms to  $\overline{t^x}$ , written  $\overline{\sigma} \sqsubseteq \overline{t^x}$ , iff for all  $i \geq 0$  and  $v \in X$  it is true that  $t_i^x(v) = 0$  implies  $v \notin x_i$  and  $t_i^x(v) = 1$  implies  $v \in x_i$ . Conformance  $\overline{\sigma} \sqsubseteq \overline{t^y}$  with the output part of the template is defined analogously. The guarantee  $g_{\text{new}}$  must be defined in such a way that it accepts a trace  $\overline{\sigma}$  iff  $\overline{\sigma} \sqsubseteq \overline{t^x}$  implies  $\overline{\sigma} \sqsubseteq \overline{t^y}$ . How  $g_{\text{new}}$  is actually constructed depends on the specification language.

Guarantee  $g_{\text{new}}$  is added to specification  $\varphi = (A, G)$  to obtain  $\varphi' = (A, G \cup g_{\text{new}})$ . If  $\varphi'$  is realizable, then  $\varphi$  is incomplete and  $\varphi'$  is a refinement which makes it more complete. If  $\varphi'$  is unrealizable, then this means that  $\varphi$  is so restrictive that no system can fulfill  $\varphi$  and the desired behavior formalized in  $g_{\text{new}}$  at the same time. Resolving this conflict between  $\varphi$  and  $g_{\text{new}}$  is equivalent to resolving unrealizability of  $\varphi'$ . The next sections will explain how unrealizable specifications are debugged.

Example 1. We use a specification of a controller for two dining philosophers  $P_0$  and  $P_1$  to illustrate our debugging method throughout this article. The system is illustrated in Fig. 5a. The inputs  $h_0$  and  $h_1$  signal to the controller that  $P_0$  or  $P_1$  is hungry. Input p indicates whether the food is poisoned. The outputs  $e_0$  and  $e_1$  are set if the respective philosopher is allowed to eat. A first version of the specification could be  $\varphi_1 = (\{a_1\}, \{g_1, g_2, g_3\})$  with

$$\begin{split} a_1 &= \mathsf{always}(p) \ \mathsf{or} \ \mathsf{always}(\mathsf{not} \, p) \\ g_1 &= \mathsf{always}(\mathsf{not}(e_0) \ \mathsf{or} \ \mathsf{not}(e_1)) \\ g_2 &= \mathsf{always}(\mathsf{eventually}(\mathsf{not}(h_0) \ \mathsf{or} \ e_0)) \\ g_3 &= \mathsf{always}(\mathsf{eventually}(\mathsf{not}(h_1) \ \mathsf{or} \ e_1)) \end{split}$$

Assumption  $a_1$  states that food is either always poisoned or never. Guarantee  $g_1$  requires that  $P_0$  and  $P_1$  do not

eat simultaneously. The guarantees  $g_2$  and  $g_3$  ensure that no philosopher starves forever. Specification  $\varphi_1$  is realizable and Fig. 5b depicts a possible simulation run. The gray background marks the part of the trace that repeats infinitely often. In this run,  $P_1$  is allowed to eat although the food is poisoned. In order to exclude this undesired behavior, the user corrects the trace as shown in Fig. 5c. The tool transforms this trace into a guarantee

$g_4 = \mathsf{always}(p) \mathsf{implies} \mathsf{always}(\mathsf{not}(e_0) \mathsf{and} \mathsf{not}(e_1))$

and refines  $\varphi_1$  to  $\varphi_2 = (\{a_1\}, \{g_1, g_2, g_3, g_4\})$ , which is unrealizable. That is,  $\varphi_1$  is in conflict with the desired behavior specified in Fig. 5c. Debugging this conflict, carried out by debugging the unrealizability of  $\varphi_2$ , will be explained in the next sections.

# 4.2 Model-Based Diagnosis for Unrealizability

This section shows how model-based diagnosis (MBD) can be applied to locate the error in an unrealizable specification. In contrast to the standard MBD setting, we do not diagnose a conflict between a system description and an observation but an inherently conflicting system description, namely the unrealizable specification.

### 4.2.1 Diagnosis of Guarantees

Let  $\varphi = (A,G)$  be an unrealizable specification over inputs X and outputs Y. Our goal for this section is to identify sets of components in  $\varphi$  that can be modified in such a way that the specification becomes realizable. The first question that naturally arises is how to define a component in this setting. A first idea could be to make all assumptions and guarantees components, i.e.,  $\mathsf{COMP}_{A,G} = A \cup G$ , because they typically define relatively self contained and independent aspects of the system behavior. However, the following problem arises with this definition.

**Proposition 1.** If a diagnosis is defined to be a minimal set  $\Delta_{A,G} \subseteq (A \cup G)$  of assumptions and guarantees which can be modified in such a way that the specification becomes realizable, then every set  $\{a\}$  for  $a \in A$  is a diagnosis.

This is a direct consequence of Eq. 4, since replacing any assumption with  $\bot$  gives a realizable specification. In other words, it does not make sense to search for assumptions that can be modified to obtain a realizable specification, because every assumption can be modified in such a way. However, not every guarantee can be changed to fix unrealizability. Therefore, we use the component definition  $\mathsf{COMP}_G = G$ , implicitly assuming that all assumptions are as intended by the designer. A complementary approach, which deals with how to find suitable environment assumptions, has been presented by Chatterjee et al. [7].

$<sup>^2</sup>$  Note that having  $g_{\rm new}$  contain an implication does not break the splitting into assumptions and guarantees. It just reflects the fact that a trace is fulfilled by  $g_{\rm new}$  if it either violates the input part or fulfills the output part of the user-given trace template.

We define the system description SD to be the tuple (A,G,X,Y). There is no observation in our setting. While standard MBD attempts to explain logical inconsistencies, we need to explain the unrealizability of a specification. As a notion of consistency we therefore define a function  $\operatorname{consistent}_G^{\operatorname{SD}}: 2^{\operatorname{COMP}_G} \to \{\operatorname{true}, \operatorname{false}\}$  as  $\operatorname{consistent}_G^{\operatorname{SD}}(G') = \operatorname{realizable}((A,G'))$ . Intuitively, this function  $\operatorname{consistent}_G^{\operatorname{SD}}$  maps a set  $G' \subseteq \operatorname{COMP}_G$  of components to true iff (A,G') is a realizable specification.

In order to bridge the gap between our definition of consistency and that of Section 3.1, which is based on normally and abnormally behaving components, we can transform  $\varphi$  to  $\tilde{\varphi}$  such that for every trace  $\overline{\sigma} \in \Sigma^{\omega}$  we have that  $\overline{\sigma} \models \tilde{\varphi}$  iff

$$(\forall a \in A . \overline{\sigma} \models a)$$

implies  $(\forall g \in G . \mathsf{AB}(g) \lor (\overline{\sigma} \models g))$ .

That is, abnormal guarantees do not have to be fulfilled in  $\tilde{\varphi}$  (cf. Eq. 4). Consequently, consistent  $_{G}^{SD}(G') = \text{true}$  iff  $\tilde{\varphi}$  is realizable with  $\neg AB(g')$  for all  $g' \in G'$ . Since guarantees that do not have to be fulfilled can be thought of being removed from the specification, this is equivalent to the simpler definition given above.

**Lemma 1.** Function consistent<sub>G</sub><sup>SD</sup> is monotonic, i.e., for all  $G'' \subseteq G' \subseteq G$  we have that  $\neg \operatorname{consistent}_G^{SD}(G'')$  implies  $\neg \operatorname{consistent}_G^{SD}(G')$ .

This is obvious since adding guarantees to an unrealizable specification preserves unrealizability. Similar to Eq. 2, a conflict is now a set  $C_G \subseteq \mathsf{COMP}_G$  such that  $\mathsf{consistent}_G^{\mathsf{SD}}(C_G) = \mathsf{false}$ , i.e.,  $\mathsf{realizable}((A, C_G)) = \mathsf{false}$ . In analogy to Eq. 1, a diagnosis is finally a minimal set  $\Delta_G \subseteq \mathsf{COMP}_G$  for which  $\mathsf{consistent}_G^{\mathsf{SD}}(\mathsf{COMP}_G \setminus \Delta_G) = \mathsf{true}$  holds.

**Observation 1** Given that  $C_G$  is a conflict in an unrealizable specification  $\varphi$ , at least one guarantee  $g \in C_G$  must be modified in order to render  $\varphi$  realizable.

If none of the guarantees in a conflict are modified, then the specification is unrealizable, independent of all other guarantees. The reason is that the guarantees in  $C_G$  already induce an unrealizable specification, additional guarantees can only make it worse (see Lemma 1).

**Observation 2** A diagnosis  $\Delta_G \subseteq G$  is a minimal set of guarantees that can be modified in such a way that the specification becomes realizable.

The guarantees  $g \in \Delta_G$  can be modified to  $\top$ , which gives a realizable specification. By definition,  $\Delta_G$  is a minimal set for which this is possible.

Example 2. Specification  $\varphi_2 = (\{a_1\}, \{g_1, g_2, g_3, g_4\})$  is unrealizable (see Example 1). It contains the minimal conflicts  $C_{G,1} = \{g_2, g_4\}$  and  $C_{G,2} = \{g_3, g_4\}$ .  $C_{G,1}$  is a conflict because  $(\{a_1\}, \{g_2, g_4\})$  is unrealizable, i.e., no system can implement both

$g_2 = \mathsf{always}(\mathsf{eventually}(\mathsf{not}(h_0) \, \mathsf{or} \, e_0)) \, \mathsf{and}$  $g_4 = \mathsf{always}(p) \, \mathsf{implies} \, \mathsf{always}(\mathsf{not}(e_0) \, \mathsf{and} \, \mathsf{not}(e_1)).$  If  $h_0$  and p are always set, the system must either violate  $g_4$  (if it ever sets  $e_0$ ) or  $g_2$  (otherwise).  $C_{G,1}$  is minimal because  $(\{a_1\}, \{g_2\})$  and  $(\{a_1\}, \{g_4\})$  are both trivially realizable. Analogously for  $C_{G,2}$ . There are more conflicts (any superset of  $C_{G,1}$  or  $C_{G,2}$ ), but no more minimal ones. The diagnoses for  $\varphi_2$  are  $\{g_4\}$  and  $\{g_2, g_3\}$ . The set  $\{g_2, g_3\}$  is a diagnosis because  $(\{a_1\}, \{g_1, \top, \top, g_4\}),$ which is equivalent to  $(\{a_1\}, \{g_1, g_4\})$ , is realizable: An implementation could forbid  $P_0$  and  $P_1$  to ever eat. This also means that  $g_2$  and  $g_3$  can be modified in such a way that the specification becomes realizable, because modifying  $g_2$  and  $g_3$  to  $\top$  certainly resolves the unrealizability. There are other, more desirable ways to weaken  $g_2$  and  $g_3$ , for instance to always(eventually(p or not( $h_0$ ) or  $e_0$ )) and always(eventually(p or not( $h_1$ ) or  $e_1$ )). The set  $\{g_4\}$ is a diagnosis because  $(\{a_1\}, \{g_1, g_2, g_3\}) = \varphi_1$  is realizable (see Example 1). MBD also tells the user that, for instance, modifying  $g_1$  alone cannot resolve the unrealizability because  $\{g_1\}$  is not a diagnosis.

#### 4.2.2 Diagnosis of Output Signals

In the previous section we defined diagnoses to be (sets of) guarantees that can be weakened in order to fix the unrealizability of a specification. In this section we define a formalism to identify output signals that may be overconstrained. We also show how the two approaches can be combined.

Let  $\varphi = (A,G)$  be an unrealizable specification of a system with inputs X and outputs Y, and let  $\overline{\sigma} = (x_0,y_0)(x_1,y_1)\ldots \in (\mathcal{X}\times\mathcal{Y})^\omega$  be a trace. We define an existential quantification  $(A,\exists Y'.G)$  of the outputs  $Y'\subseteq Y$  in the guarantees G of  $\varphi$  in such a way that  $\overline{\sigma}\models (A,\exists Y'.G)$  iff

$$(\forall a \in A . \overline{\sigma} \models a)$$

implies  $(\forall g \in G . \overline{\sigma} \models \exists Y' . g)$ .

The existential quantification  $\exists Y' \cdot g$  in one single guarantee  $g \in G$  is defined as  $\overline{\sigma} \models \exists Y' \cdot g$  iff

$$\exists y_0' y_1' y_2' \dots \in (2^{Y'})^{\omega} . (x_0, y_0^E)(x_1, y_1^E)(x_2, y_2^E) \dots \models g,$$

where  $y_i^E = (y_i \setminus Y') \cup y_i'$  for all  $i \geq 0$ .

Informally speaking, a quantification  $\exists Y' . G$  of outputs  $Y' \subseteq Y$  in guarantees G removes all restrictions on these outputs. The specification  $(A,\exists Y' . G')$  allows arbitrary values for all signals  $y \in Y'$  in all time steps. Also note that the quantification is performed on every single guarantee in isolation, and not for all guarantees simultaneously. With  $\mathsf{SD} = (A,G,X,Y)$ ,  $\mathsf{COMP}_Y = Y$  and  $Y' \subseteq Y$ , we define consistent  $\mathsf{SD}_Y(Y') = \mathsf{realizable}((A,\exists Y \setminus Y' . G))$ . Consequently, a conflict is a set  $C_Y \subseteq Y$  of outputs for which  $\mathsf{realizable}((A,\exists Y \setminus C_Y . G)) = \mathsf{false}$  applies. Finally, a diagnosis is a minimal set  $\Delta_Y \subseteq Y$  such that  $\mathsf{realizable}((A,\exists \Delta_Y . G)) = \mathsf{true}$ . Hence, every diagnosis  $\Delta_Y$  represents a minimal set of signals that may be overconstrained, because removing restrictions on these signals resolves unrealizability.

An alternative version  $\tilde{\exists}$  of the quantification can be defined in such a way that  $\overline{\sigma} \models (A, \tilde{\exists} Y', G)$  iff

$$(\forall a \in A . \overline{\sigma} \models a) \text{ implies } \overline{\sigma} \models \widetilde{\exists} Y' . G,$$

where  $\overline{\sigma} \models \widetilde{\exists} Y' \cdot G$  iff

$$\exists y_0'y_1'\ldots \in \left(2^{Y'}\right)^{\omega}. \forall g \in G.(x_0, y_0^E)(x_1, y_1^E)\ldots \models g,$$

and  $y_i^E$  is again  $(y_i \setminus Y') \cup y_i'$  for all  $i \geq 0$ .

The difference is that  $\exists$  is performed on every guarantee separately, while  $\tilde{\exists}$  requires the existence of one trace of the quantified signals fulfilling all guarantees.

Example 3. As an illustration, consider the specification  $(A,G)=(\emptyset,\{\mathsf{always}(O),\mathsf{always}(\mathsf{not}\,O)\}),$  where O is the only output. The specification  $(A,\exists\{O\}\,.\,G)$  is realizable (it allows all traces), but  $(A,\bar{\exists}\{O\}\,.\,G)$  is not. Consequently,  $\{O\}$  is a diagnosis when using  $\bar{\exists}$  but not when using  $\bar{\exists}$ .

Our approach works for both definitions. However, we decided for  $\exists$  because we think that  $\{O\}$  should be a diagnosis for the example. After all, if there was no output O, there would also be no conflict. Furthermore, the user can often comprehend what a quantification in one guarantee means. Understanding what a simultaneous quantification in all guarantees means is typically much more difficult, because complex dependencies between the guarantees may exist.

# 4.2.3 Diagnosis of Guarantees and Outputs

The approaches of diagnosing guarantees and outputs can also be combined by defining  $\mathsf{COMP}_{G,Y} = G \cup Y$ . For  $B \subseteq \mathsf{COMP}_{G,Y}$  we have that  $\mathsf{consistent}_{G,Y}^{\mathsf{SD}}(B) = \mathsf{realizable}((A,\exists Y \setminus B . (G \cap B)))$ . Moreover,  $C_{G,Y} \subseteq (Y \cup G)$  is a conflict iff  $\mathsf{realizable}((A,\exists Y \setminus C_{G,Y} . (G \cap C_{G,Y}))) = \mathsf{false}$ . A diagnosis is finally a minimal set  $\Delta_{G,Y} \subseteq (Y \cup G)$  such that  $\mathsf{realizable}((A,\exists (Y \cap \Delta_{G,Y}) . (G \setminus \Delta_{G,Y}))) = \mathsf{true}$ . The properties stated in Section 4.2.1 still hold:

**Lemma 2.** Function consistent  $_{G,Y}^{SD}$  is monotonic in the sense that, for all  $B'' \subseteq B' \subseteq G \cup Y$ , we have that  $\neg \operatorname{consistent}_{G,Y}^{SD}(B'')$  implies  $\neg \operatorname{consistent}_{G,Y}^{SD}(B')$ .

In analogy to the Observations 1 and 2, one has to weaken at least one guarantee or output signal out of every conflict  $C_{G,Y}$  in order to obtain a realizable specification. A diagnosis  $\Delta_{G,Y}$  is a minimal set of guarantees and output signal definitions that can be modified to obtain a realizable specification.

**Theorem 1.** Every diagnosis  $\Delta_G$  and every diagnosis  $\Delta_Y$  for an unrealizable specification  $\varphi = (A, G)$  is also a diagnosis with respect to the definition of  $\Delta_{G,Y}$ .

*Proof.* If  $\operatorname{realizable}((A,G\setminus\Delta_G))$  holds, then so does  $\operatorname{realizable}((A,\exists(Y\cap\Delta_G).(G\setminus\Delta_G)))$  because  $Y\cap\Delta_G=\emptyset$ . Moreover,  $\forall\Delta_G'\subset\Delta_G$ .  $\neg\operatorname{realizable}((A,G\setminus\Delta_G'))$  implies

$\begin{array}{l} \forall \Delta'_G \subset \Delta_G \, . \, \neg \, \mathsf{realizable}((A, \exists (Y \cap \Delta'_G) \, . (G \setminus \Delta'_G))) \, \mathsf{since} \\ Y \cap \Delta'_G = \emptyset. \, \mathsf{Hence}, \, \mathsf{any} \, \Delta_G \, \mathsf{is} \, \mathsf{also} \, \mathsf{a} \, \mathsf{diagnosis} \, \Delta_{G,Y}. \\ \mathsf{Analogously}, \, \mathsf{since} \, \, Y \cap \Delta''_Y = \Delta''_Y \, \mathsf{and} \, \, G \setminus \Delta''_Y = G \\ \mathsf{for} \, \mathsf{all} \, \, \Delta''_Y \subseteq \Delta_Y, \, \mathsf{we} \, \mathsf{have} \, \mathsf{that} \, \, \mathsf{realizable}((A, \exists \Delta_Y \, . G)) \\ \mathsf{implies} \, \, \mathsf{that} \, \, \, \mathsf{realizable}((A, \exists (Y \cap \Delta_Y) \, . (G \setminus \Delta_Y))) \, \, \mathsf{and} \\ \forall \Delta'_Y \subset \Delta_Y \, . \, \neg \, \mathsf{realizable}((A, \exists \Delta'_Y \, . G)) \, \, \mathsf{implies} \, \, \forall \Delta'_Y \subset \Delta_Y \, . \, \neg \, \mathsf{realizable}((A, \exists (Y \cap \Delta'_Y) \, . (G \setminus \Delta'_Y))) \, \, . \, \, \mathsf{Therefore}, \\ \mathsf{every} \, \, \mathsf{diagnosis} \, \Delta_Y \, \, \mathsf{is} \, \, \mathsf{also} \, \mathsf{a} \, \, \mathsf{diagnosis} \, \Delta_{G,Y}. \quad \Box \\ \end{array}$

Theorem 1 states that the definition of  $\Delta_{G,Y}$  subsumes  $\Delta_G$  and  $\Delta_Y$ . Having all diagnoses  $\Delta_{G,Y}$ , one would not gain further diagnoses by computing  $\Delta_Y$  and  $\Delta_G$ . Thus, we will stick to the definition of  $\Delta_{G,Y}$  in the following.

Example 4. The minimal conflicts for the unrealizable specification  $\varphi_2 = (\{a_1\}, \{g_1, g_2, g_3, g_4\})$  from Example 1 are  $\{g_2, g_4, e_0\}$  and  $\{g_3, g_4, e_1\}$ . Recall that

```

g_2 = \text{always}(\text{eventually}(\text{not}(h_0) \text{ or } e_0)) \text{ and } g_4 = \text{always}(p) \text{ implies always}(\text{not}(e_0) \text{ and not}(e_1)).

```

The set  $\{g_2, g_4, e_0\}$  is a conflict because the specification  $(\{a_1\}, \exists e_1. \{g_2, g_4\})$  is equivalent to

$$\begin{aligned} (\{a_1\}, \ \, &\{\mathsf{always}(\mathsf{eventually}(\mathsf{not}(h_0) \ \mathsf{or} \ e_0)), \\ &\mathsf{always}(p) \ \mathsf{implies} \ \mathsf{always}(\mathsf{not} \ e_0)\}) \end{aligned}$$

and thus unrealizable. Similar for  $\{g_3,g_4,e_1\}$ . The diagnoses are  $\{g_4\}$ ,  $\{g_2,g_3\}$ ,  $\{g_2,e_1\}$ ,  $\{e_0,g_3\}$ , and  $\{e_0,e_1\}$ . Note that the diagnoses are exactly the minimal hitting sets for the minimal conflicts, i.e., every diagnosis shares at least one element with every minimal conflict.

### 4.2.4 Computation of Diagnoses

So far, we have only defined what diagnoses are. This section addresses their computation. We use the algorithm presented by Reiter [41] for the computation of diagnoses. It computes all minimal hitting sets for the collection of conflicts via a hitting set tree. Theorem 2, which is a reformulation of Theorem 4.4 in [41], ensures that this procedure correctly yields all diagnoses.

**Theorem 2.** A set  $\Delta_{G,Y} \subseteq G \cup Y$  is a diagnosis for an unrealizable specification  $\varphi = (A, G)$  iff it is a minimal hitting set for the collection K of conflicts in  $\varphi = (A, G)$ .

Proof. ( $\Rightarrow$ ) Let  $\Delta_{G,Y}$  be a diagnosis. We have that  $\mathsf{consistent}_{G,Y}^{\mathsf{SD}}((G \cup Y) \setminus \Delta_{G,Y})$  holds. Consequently, due to Lemma 2, there is no conflict not containing an element of  $\Delta_{G,Y}$ . Hence,  $\Delta_{G,Y}$  is a hitting set for  $\mathcal{K}$ . It is a minimal hitting set because for all  $\Delta'_{G,Y} \subset \Delta_{G,Y}$  we have that  $\neg \mathsf{consistent}_{G,Y}^{\mathsf{SD}}((G \cup Y) \setminus \Delta'_{G,Y})$  holds by definition. That is, for all real subsets  $\Delta'_{G,Y}$  of  $\Delta_{G,Y}$  there exists at least one conflict which does not contain any element of  $\Delta'_{G,Y}$ . Hence,  $\Delta_{G,Y}$  is a minimal hitting set.

( $\Leftarrow$ ) Let  $\Delta_{G,Y}$  be a minimal hitting set for  $\mathcal{K}$ . By definition,  $\Delta_{G,Y}$  is also a diagnosis iff  $\mathsf{consistent}_{G,Y}^{\mathsf{SD}}((G \cup Y) \setminus \Delta_{G,Y})$  and  $\neg \mathsf{consistent}_{G,Y}^{\mathsf{SD}}((G \cup Y) \setminus \Delta_{G,Y}')$  hold for

all  $\Delta'_{G,Y} \subset \Delta_{G,Y}$ . Both properties are shown by contradiction. If the former would not hold, there would be a conflict not containing any element of  $\Delta_{G,Y}$ , so  $\Delta_{G,Y}$  would not be a hitting set for  $\mathcal{K}$ . If the latter would not hold, then  $\Delta'_{G,Y} \subset \Delta_{G,Y}$  would a hitting set for  $\mathcal{K}$  (see  $(\Rightarrow)$ ), so  $\Delta_{G,Y}$  could not be a minimal hitting set.  $\square$

Since understanding the hitting set tree algorithm is not vital for the purpose of this article, we refer the reader to [41] for details. Basically, the algorithm only requires a procedure to compute a conflict not containing a certain set of components, if such a conflict exists. This can be implemented with one single realizability check. However, the algorithm performs better if the computed conflicts are minimal. Such a procedure can be defined as  $\mathsf{cNot}^\mathsf{SD}(B) =$

$$\begin{cases} \text{None} & \text{if consistent}_{G,Y}^{\mathsf{SD}}(\mathsf{COMP}_{G,Y} \setminus B) \\ \mathsf{min}^{\mathsf{SD}}(\mathsf{COMP}_{G,Y} \setminus B) & \text{otherwise} \end{cases}$$

for  $B\subseteq \mathsf{COMP}_{G,Y}.$  The function  $\mathsf{min^{SD}}$  computes the minimal conflict. That is, given a set  $M\subseteq \mathsf{COMP}_{G,Y}$  such that  $\mathsf{consistent_{G,Y}^{SD}}(M)=\mathsf{false},$  it computes a set  $\hat{M}=\mathsf{min^{SD}}(M)$  such that  $\mathsf{consistent_{G,Y}^{SD}}(\hat{M})=\mathsf{false},$  and for all  $M'\subset \hat{M}$  it holds that  $\mathsf{consistent_{G,Y}^{SD}}(M')=\mathsf{true}.$  Function  $\mathsf{min^{SD}}$  can be implemented as  $\mathsf{min^{SD}}(M)=\mathsf{ddmin^{test^{SD}}}(M)$  or  $\mathsf{min^{SD}}(M)=\mathsf{linMin^{test^{SD}}}(M),$  in which  $\mathsf{test^{SD}}(M')=\mathsf{X}$  iff  $\neg \mathsf{consistent_{G,Y}^{SD}}(M').$

# 4.2.5 Performance Optimizations

Model-based diagnosis for unrealizability requires the computation of many unrealizable cores, which in turn requires many realizability checks. Hence, it is important that these operations are implemented efficiently.

The first factor which influences performance is the minimization algorithm that is used for unrealizable core computation. We propose to use Delta Debugging, as it performs much better than linMin in our experiments. (See Section 7.) Furthermore, it is important to exploit the monotonicity of test (cf. Lemma 2) to speed up the minimization as suggested in [50]: all sets M' for which test<sup>SD</sup>(M') returned  $\mathbf{X}$  are stored. Whenever a subset M'' of a stored set M' is tested, test<sup>SD</sup>(M'')  $\neq \mathbf{X}$  can be concluded without actually invoking the realizability check.

As a second performance optimization, we propose to use approximations of realizability. We call a procedure  $\operatorname{realizable}_O$  an over-approximation of  $\operatorname{realizable}(\varphi)$  implies  $\operatorname{realizable}_O(\varphi)$ . Similarly,  $\operatorname{realizable}_U$  is an underapproximation of  $\operatorname{realizable}(\varphi)$  implies  $\operatorname{realizable}(\varphi)$  for all  $\varphi$ . If the specification can be transformed into a game  $\mathcal{G}=(Q,\Sigma,T,q_0,\operatorname{Win})$ , then  $\operatorname{realizablity}$  can be decided by computing the winning region  $W_{\operatorname{sys}}\subseteq Q$  of the system and testing whether  $q_0\in W_{\operatorname{sys}}$ . An over-approximation for realizability can be defined

by computing an over-approximation  $W_O$  of  $W_{\rm sys}$  (such that  $W_O \supseteq W_{\rm sys}$ ), and checking whether  $q_0 \in W_O$ . An under-approximation can be defined analogously. Suppose that we are able to find approximations of realizability which are both fast to compute and close to the exact definition of realizability. Then we can use them to define

$$\mathsf{realizable}_E(\varphi) = \begin{cases} \mathsf{true} & \text{if } \mathsf{realizable}_U(\varphi) \\ \mathsf{false} & \text{else if } \neg \mathsf{realizable}_O(\varphi) \\ \mathsf{realizable}(\varphi) & \text{otherwise} \end{cases}$$

as an often faster decision procedure for realizability. Different approximations can be applied in different order.

An over-approximation of realizability can also be used to compute unrealizable cores in a two step approach. First, the unrealizable specification is minimized with realizable<sub>O</sub>. This gives an over-approximation of a minimal unrealizable core. In a second step, the approximate minimal core is further minimized with the exact definition of realizability, resulting in an exact minimal core. This two-step approach can be faster because ideally the expensive exact checks are performed on relatively small subsets of the specification only. More formally, we suggest to compute

$$\hat{M} = \mathsf{min}^{\mathsf{SD}}(M) = \mathsf{linMin}^{\mathsf{test}_2^{\mathsf{SD}}}\left(\mathsf{ddmin}^{\mathsf{test}_1^{\mathsf{SD}}}(M)\right) \text{ with }$$

$\mathsf{test}_1^{\mathsf{SD}}(M') = \mathbf{X} \; \mathsf{iff} \; \neg \, \mathsf{realizable}_O((A, \exists (Y \backslash M') \, . \, G \cap M')), \\ \mathsf{test}_2^{\mathsf{SD}}(M') = \mathbf{X} \; \mathsf{iff} \; \neg \, \mathsf{realizable}_E((A, \exists (Y \backslash M') \, . \, G \cap M')), \\ \mathsf{and} \; M' \subseteq M \subseteq G \cup Y. \; \mathsf{We} \; \mathsf{use} \; \mathsf{linMin} \; \mathsf{as} \; \mathsf{minimization} \\ \mathsf{algorithm} \; \mathsf{for} \; \mathsf{the} \; \mathsf{second} \; \mathsf{step}, \; \mathsf{because} \; \mathsf{ddmin} \; \mathsf{does} \; \mathsf{not} \\ \mathsf{perform} \; \mathsf{well} \; \mathsf{when} \; \mathsf{executed} \; \mathsf{on} \; \mathsf{an} \; \mathsf{almost} \; \mathsf{minimal} \; \mathsf{set} \mathsf{:} \\ \mathsf{In} \; \mathsf{the} \; \mathsf{early} \; \mathsf{phase}, \; \mathsf{all} \; \mathsf{attempts} \; \mathsf{to} \; \mathsf{remove} \; \mathsf{big} \; \mathsf{chunks} \\ \mathsf{of} \; \mathsf{the} \; \mathsf{set} \; \mathsf{fail}, \; \mathsf{so} \; \mathsf{a} \; \mathsf{lot} \; \mathsf{of} \; \mathsf{checks} \; \mathsf{are} \; \mathsf{wasted} \; \mathsf{until} \; \mathsf{the} \\ \mathsf{granularity} \; \mathsf{is} \; \mathsf{high} \; \mathsf{enough}. \; \mathsf{With} \; \mathsf{high} \; \mathsf{granularity}, \; \mathsf{ddmin} \\ \mathsf{behaves} \; \mathsf{similarly} \; \mathsf{to} \; \mathsf{linMin}.$

# 4.3 Explaining Conflicts with Counterstrategies

In the previous section, we discussed how model-based diagnosis can be used to identify possible error locations by identifying output signals and guarantees that can be weakened in order to make the specification unrealizable. However, there may be many such diagnoses and there are also many ways to weaken guarantees and restrictions on outputs. In order to find the best suitable fix, the user has to understand the problem in the specification. We assist the user in achieving this by explaining conflicts, as computed by the diagnosis algorithm, with counterstrategies.

# 4.3.1 Debugging Flow

Fig. 6 depicts the flow of our method to explain conflicts, and thereby the root causes of unrealizability. The focus is on obtaining *simple* explanations. Minimal conflicts as computed by our diagnosis algorithm are unrealizable

Fig. 6: Our procedure to explain conflicts in a specification.

cores, i.e., parts of the specification which are unrealizable on their own. First, a counterstrategy is computed not for the original specification but for an unrealizable core. Next, we use a heuristic algorithm to further simplify the counterstrategy to a countertrace, i.e., a single trace of inputs that suffices to illustrate unrealizability. Finally, we use this countertrace (or the counterstrategy, in case our heuristic fails) in an interactive diagnostic game against the user, and to compute a graph which summarizes all plays that are possible in this game. The next subsections will detail these steps.

# 4.3.2 Unrealizable Cores

Understanding the contradiction in a large unrealizable specification may be difficult, but often only a small part of the specification is responsible for the contradiction. Removing the rest gives a specification which still contains the contradiction, but is much smaller and thus easier to debug. A part of the specification which is unrealizable on its own right is called an unrealizable core [11]. For an unrealizable specification  $\varphi = (A, G)$  with inputs X and outputs Y, a minimal conflict  $C_{G,Y}$ , as computed in our diagnosis approach, represents the unrealizable core  $(A, \exists Y \setminus C_{G,Y}.(G \cap C_{G,Y}))$ . There are two important differences to unrealizable cores as defined in [11].

First, we do not remove environment assumptions. The reason is not only that Prop. 1 hinders us from defining assumptions to be components. Removing environment assumptions would also confuse the user in subsequent steps of our debugging process: the counterstrategy, computed to explain the unrealizable core, could exhibit behavior which the user originally forbade. This would allow cheating by the environment in the diagnostic game, at least from the user's point of view.

Second, using existential quantification, we not only remove properties but also output signals from the specification. The meaning is that the core is still unrealizable, even though the system can set all existentially quantified outputs arbitrarily. Again, the reason for removing outputs is not only that we wanted to identify overconstrained signals when doing diagnosis. Removing outputs also allows the user to focus on the remaining signals, which makes the diagnostic game much simpler. The quantified outputs are not even included in the game, because they can be set arbitrarily. In fact, we found that minimizing only guarantees often makes the diagnostic game more difficult. This is due to the

fact that removing guarantees gives the system more freedom. Thus, there are more possible moves and more plays to explore in the diagnostic game. Removing outputs counteracts by providing the user with choices for relevant signals only.

**Theorem 3.** Let  $\varphi = (A, G)$  be an unrealizable specification, and let  $\varphi' = (A, \exists Y'.G')$ , with  $Y' \subseteq Y$  and  $G' \subseteq G$ , be an unrealizable core thereof. Any implementation  $M^o$  of a counterstrategy for  $\varphi'$  implements a counterstrategy for  $\varphi$  as well.

*Proof.* Since  $M^o$  implements a counterstrategy for  $\varphi'$ ,  $\overline{\sigma} \not\models \varphi'$  holds for all  $\overline{\sigma} \in L(M^o)$ . Clearly,  $\varphi$  is stricter than  $\varphi'$ , i.e.,  $\overline{\sigma} \not\models \varphi'$  implies  $\overline{\sigma} \not\models \varphi$  for all  $\overline{\sigma} \in \Sigma^\omega$ . Therefore,  $\overline{\sigma} \not\models \varphi$  for all  $\overline{\sigma} \in L(M^o)$ , which means that  $M^o$  implements a counterstrategy for  $\varphi$ .  $\square$

Theorem 3 states that computing a counterstrategy for an unrealizable core is indeed useful, because any implementation of the counterstrategy can also explain the unrealizability of the original specification.

Example 5. The minimal conflict  $\{g_2, g_4, e_0\}$  (see Example 4) in specification  $\varphi_2 = (\{a_1\}, \{g_1, g_2, g_3, g_4\})$  represents the unrealizable core  $\varphi' = (\{a_1\}, \exists e_1. \{g_2, g_4\})$ . This means that  $\varphi_2$  is unrealizable even if  $g_1$  and  $g_3$  do not have to be fulfilled and  $e_1$  can be chosen completely arbitrarily in all time steps. In the diagnostic game, the user can focus on setting  $e_0$  in such a way that

$$arphi' = (\{a_1\}, \ \, \{\mathsf{always}(\mathsf{eventually}(\mathsf{not}(h_0) \, \mathsf{or} \, e_0)), \\ \mathsf{always}(p) \, \mathsf{implies} \, \mathsf{always}(\mathsf{not} \, e_0)\})$$

is fulfilled, i.e., she can focus on properties and signals that actually contribute to the conflict. Nevertheless, she will not win the game because a counterstrategy could set p and  $h_0$  in all steps. This is also a valid counterstrategy for  $\varphi_2$ . The unrealizable core just makes the task of the user easier.

#### 4.3.3 Countertraces

One of the main sources for complexity in the diagnostic game is that the environment behavior, defined by the counterstrategy, depends on the previous behavior of the system. The user would prefer one single trace  $\overline{\tau} \in \mathcal{X}^{\omega}$  of inputs such that no output trace  $\overline{y} \in \mathcal{Y}^{\omega}$  can make  $(\overline{\tau}||\overline{y})$  fulfill the specification. We call such a trace  $\overline{\tau}$  a countertrace. A countertrace significantly reduces the effort of understanding which environment behavior causes problems.

Unfortunately, a countertrace does not always exist. Consider the specification  $(\emptyset, \{\mathsf{always}(y \; \mathsf{iff} \; \mathsf{next} \, x)\})$ , where x and y are Boolean inputs and outputs, respectively. The specification is unrealizable, because the system would have to look into the future to comply with it. However, for every input trace there is also an output trace such that the specification is fulfilled (namely

the input trace shifted by one step into the future) [42, 37]. As a second difficulty, computing countertraces is expensive. In general, we can compute a countertrace by existentially quantifying outputs from the game automaton, and complementing the resulting automaton. Every trace in the language of the complemented automaton is a valid countertrace. However, complementation would cause an exponential blow-up since the automaton may be non-deterministic after quantification. We consider this unacceptable, and therefore define a heuristic algorithm. It does not always find a countertrace, even if one exists. However, our experiments show that it is fast and often successful.

Our heuristic takes a counterstrategy  $\mathcal{S} = (\Gamma, \gamma_0, \rho)$  with  $\rho \subseteq (Q \times \Gamma \times \mathcal{X} \times \Gamma)$  for game  $\mathcal{G} = (Q, \Sigma, T, q_0, \mathsf{Win})$ , constructed from an unrealizable specification  $\varphi$ . The construction of these elements depends on the specification language used. For every state  $q \in Q$  and memory content  $\gamma \in \Gamma$ , the counterstrategy defines possible inputs  $x \in \mathcal{X}$  and next memory contents  $\gamma' \in \Gamma$  by enforcing that  $(q, \gamma, x, \gamma') \in \rho$ . After the selection of such an input, the output is chosen by the system. The idea of our heuristic is that we choose from the inputs allowed by the counterstrategy in such a way that the next choice of an input is independent of the choice of the output.

We compute the countertrace  $\overline{\tau} = \tau_0 \tau_1 \ldots \in \mathcal{X}^{\omega}$  and a sequence  $S_0 S_1 \ldots$  of sets  $S_i \subseteq (Q \times \Gamma)$  in parallel. Every  $S_i$  contains all pairs of state and memory content which are possible after the finite input sequence  $\tau_0 \ldots \tau_{i-1}$ . The computation starts with  $S_0 = \{(q_0, \gamma_0)\}$  and proceeds with

$$S_{i+1} = \{ (q', \gamma') \mid \exists (q, \gamma) \in S_i, y \in \mathcal{Y} .$$

$$q' = T(q, (\tau_i, y)) \land (q, \gamma, \tau_i, \gamma') \in \rho \},$$

where  $\tau_i$  is chosen arbitrarily from the set  $T_i = \{\tau \in \mathcal{X} \mid \forall (q,\gamma) \in S_i . \exists \gamma' \in \Gamma . (q,\gamma,\tau,\gamma') \in \rho\}$ . The set  $T_i$  contains all inputs which conform to the counterstrategy, independent of the current state and memory content  $(q,\gamma) \in S_i$ . We choose such an input  $\tau_i \in T_i$  for the countertrace, compute with  $S_{i+1}$  all state-memory pairs in which we might end up in the next step, and repeat the procedure. This gives an input trace  $\overline{\tau} = \tau_0 \tau_1 \dots$  which conforms to the counterstrategy, independent of the outputs chosen by the system.

If  $T_i = \emptyset$  for any i, our heuristic fails. We can stop the computation successfully at index k if  $S_k \subseteq S_j$  for some j < k. This is because  $S_k \subseteq S_j$  implies  $T_k \supseteq T_j$ , and thus,  $\tau_k$  can be set to  $\tau_j$ . Since the definition of  $S_{i+1}$  is monotonic in  $S_i$  (when used with the same  $\tau_i$ ), we have that  $S_{k+1} \subseteq S_{j+1}$ , which implies  $T_{k+1} \supseteq T_{j+1}$  and allows  $\tau_{k+1} = \tau_{j+1}$ . This can be repeated. We obtain a lasso-shaped countertrace with finite stem  $\tau_0 \dots \tau_{j-1}$  followed by infinitely many repetitions of  $\tau_j \dots \tau_{k-1}$ . A symbolic implementation (e.g., using BDDs) of the computation is straightforward if  $\mathcal G$  and  $\mathcal S$  are represented symbolically.

The number of iterations is equal to the length (stem plus loop) of the computed countertrace. In the worst case, our heuristic requires  $2^{|Q \times \Gamma|} - 1$  iterations. However, in all our experiments the length of the countertrace was below 10. The intuitive explanation of the good performance in practice is that existing synthesis algorithms often yield strategies that respond within short time, and the computed countertrace can only exhibit behavior allowed by the counterstrategy.

Even if a countertrace exists, our algorithm may be unable to find one. There are two reasons. First, it may fail due to a bad choice of an input letter  $\tau_i \in T_i$ . This problem can be solved with backtracking. The second reason is that the counterstrategy from which the countertrace is created may not contain all possible ways to force the system to violate the specification.

A countertrace with finite stem  $\tau_0 \dots \tau_{j-1}$  and infinite loop  $\tau_j \dots \tau_{k-1}$  can be interpreted as a strategy  $S_{\overline{\tau}} = (\Gamma_{\overline{\tau}}, 0, \rho_{\overline{\tau}})$  with  $\Gamma_{\overline{\tau}} = \{0, \dots, k-1\}$  and

$$\rho_{\overline{\tau}} = \left\{ (q, \gamma, \tau_{\gamma}, next(\gamma)) \in (Q, \Gamma_{\overline{\tau}}, \mathcal{X}, \Gamma_{\overline{\tau}}) \right\}, \text{ where}$$

$$next(\gamma) = \begin{cases} j & \text{if } \gamma = k - 1, \text{ and} \\ \gamma + 1 & \text{otherwise.} \end{cases}$$

**Theorem 4.** Every play  $\overline{\pi}$  that conforms to the countertrace  $\overline{\tau}$ , i.e., which conforms to the strategy  $S_{\overline{\tau}} = (\Gamma_{\overline{\tau}}, 0, \rho_{\overline{\tau}})$  is won by the environment.

*Proof.* The inputs  $\tau_i$  dictated by countertrace  $\overline{\tau}$  and also by  $\rho_{\overline{\tau}}$  are (singleton) subsets of the inputs that are allowed by the counterstrategy  $\mathcal{S} = (\Gamma, \gamma_0, \rho)$ . This follows trivially from the construction of  $\overline{\tau}$  and  $\mathcal{S}_{\overline{\tau}}$ . Since all plays conforming to  $\mathcal{S}$  are won by the environment, so are all plays conforming to  $\overline{\tau}$  and  $\mathcal{S}_{\overline{\tau}}$ .  $\square$

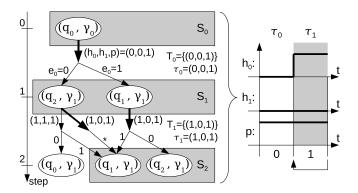

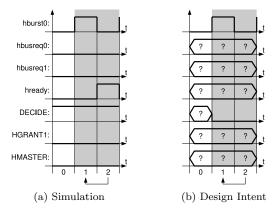

Example 6. We apply our algorithm to compute a countertrace for the unrealizable core  $(\{a_1\}, \exists e_1. \{g_2, g_4\}) =$

$$(\{a_1\}, \{always(eventually(not(h_0) or e_0)), always(p) implies always(not e_0)\}),$$

which was introduced in Example 5. Due to space constraints, we neither provide a full game definition  $\mathcal{G}$  nor a full counterstrategy definition  $\mathcal{S}$ . Instead, we present parts of these elements in a way that best serves the explanation. Our algorithm is illustrated in Fig. 7. It starts with  $S_0 = \{(q_0, \gamma_0)\}$ . From there, the counterstrategy only allows the input letter  $(h_0, h_1, p) = (0, 0, 1)$ . Hence,  $T_0 = \{(0,0,1)\}\$ and  $\tau_0$  can only be set to (0,0,1). With input  $(h_0, h_1, p) = (0, 0, 1)$ , the system has two possibilities. If it sets  $e_0 = 0$ , the play will get to statememory pair  $(q_2, \gamma_1)$ . With  $e_0 = 1$  it goes to  $(q_1, \gamma_1)$ . After one step, the play is either in  $(q_2, \gamma_1)$  or  $(q_1, \gamma_1)$ , so  $S_1 = \{(q_2, \gamma_1), (q_1, \gamma_1)\}$ . From  $(q_2, \gamma_1)$ , the counterstrategy allows two input letters, namely  $(h_0, h_1, p) = (1, 1, 1)$ and (1,0,1). From  $(q_1,\gamma_1)$  only (1,0,1) is allowed.  $T_1$ consists of input letters that are allowed from all elements of  $S_1$ , so  $T_1 = \{(1,0,1)\}$ . Consequently, there is no other possibility than setting  $\tau_1 = (1, 0, 1)$ . With input (1,0,1) in Step 1,  $(q_1,\gamma_1)$  and  $(q_2,\gamma_1)$  are the only possible successors. Hence,  $S_2 = \{(q_1, \gamma_1), (q_2, \gamma_1)\}$ . Since

Fig. 7: An example illustrating countertrace computation.

$S_2 = S_1$ , the algorithm terminates successfully. This is possible because all  $\tau_i$  with  $i \geq 2$  could be set to  $\tau_1$ , with the consequence that all encountered sets  $S_i$  with i > 2 would be equal to  $S_1$ . Therefore, the countertrace is  $\tau_0$  followed by infinitely many repetitions of  $\tau_1$ . This is depicted on the right-hand side of Fig. 7.

# 4.4 Interactive Diagnostic Games and Graphs

We allow the user to play an interactive diagnostic game against the counterstrategy. In every step, the counterstrategy provides inputs and the user responds with outputs. The user attempts to fulfill the specification but fails for sure. Playing the game (and losing repeatedly) will help the user understand why she cannot win, i.e., why the specification is unrealizable. If a countertrace is found, the user plays against this trace. The entire trace is shown right from the beginning to clearly set out the problematic environment behavior.

In order to speed up the learning process, we also provide the user with a graph  $\mathbb G$  which summarizes all plays that are possible against the counterstrategy. Every node in the graph corresponds to a reachable statememory pair  $(q,\gamma)\in(Q,\Gamma)$ . There is a special start node  $(q_0,\gamma_0)$ . Directed edges between nodes are created if the corresponding transition is possible. Edges are labeled with the inputs and outputs that enable the transition. The graph can serve as a "cheat sheet" for the diagnostic game. The user can see already in advance how the counterstrategy will react to her moves. Hence, she might discard some moves without trying them in the game. This reduces the time necessary to understand the cause for unrealizability.

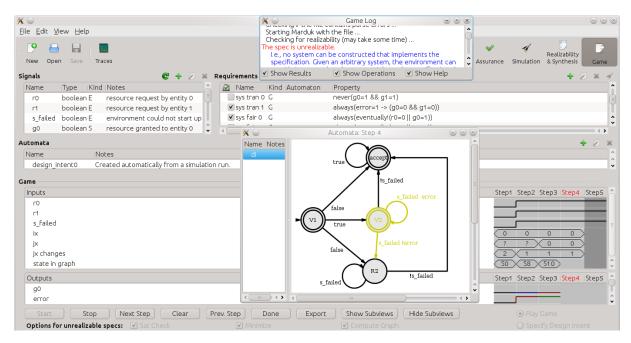

# 5 Debugging GR(1) Specifications